Noida end of Magma helps 'finish' chip design

Indian innovation saluted at annual MUSIC developer event

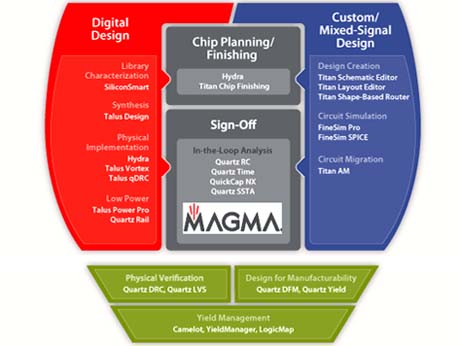

Bangalore May 7: The upcoming new edition of Talus Design, the full-chip synthesis tool offered by Indian-co-founded , US-based electronic design automation leader, Magma Design Automation ( www.magma-da.com) , promises to clip typical design cycle times from a typical 90 hours to something around 36, while the next iteration will further this time to half. Unveiled at the company’s annual India-based Magma Users Summit on IC (MUSIC) in Bangalore, the new Talus available this month, offers an enhanced timing optimization engine, improved usability features and new support for third party design-for-test products.

In an important endorsement for the company, the world’s largest contract chip maker, Taiwan-based TSMC, says the use of Magma’s Titan Analog Migration tool allowed designers to shorten the time for porting new designs and to optimize analog circuits so that they took up less space on the silicon and consumed less power.

Co-founded by Rajeev Madhavan ( today, Chairman and CEO) in 1997, Magma has offices in Bangalore, Mumbai and Noida which account for a quarter of its total strength and includes significant R&D muscle.

The Bangalore MUSIC event saluted Indian innovation in chip design automation by recognizing the best tech papers submitted for the conference.

The top paper award went to Sai Dhiraj Korada of Qualcomm for his paper entitled “Multi-Mode/Multi-Corner Techniques for 45-nm Designs Using Talus®.”

The second place award went to Thrivikraman M of Rambus for “A Configurable and Automated Approach for High-Speed, Custom-Digital Design.”

The third place was jointly shared by Arun Kothiyar of Texas Instruments for “The Talus Sign-Off Flow and Optimization Methodology” and Murali Rajagopalan of Open Silicon India for “Concurrent Leakage Power and Timing Optimization Using Talus.”

The winning papers were selected by conference attendees and the MUSIC Technical Program Committee from designers at academic institutions as well as technology companies, including ARM, Qualcomm and Texas Instruments.

The MUSIC event was steered as always by IIT Madras’ Prof V Kamakoti whose group is one of India’s best semiconductor and ASIC design resources in academia. The group has put together a cool tool called Magma For You in Three Hours -- MYTH.

Speaking to IndiaTechOnline on the sidelines of the conference, Magma’s Vice President ( R&D) Vivek Raghavan said the Noida based development team contributes significantly to chip finishing software routines. Ricky Bedi, Vice President, Application Engineering, said the Magma roadmap would embrace tomorrow’s megachips with 100 million plus gates and gate blocks of 10 million each. The R&D focus was already moving ahead from 32 nanometer to 28 nanometer designs, he added.

- Anand Parthasarathy